possessiones uber:

| EXEMPLUM | PERSEQUOR |

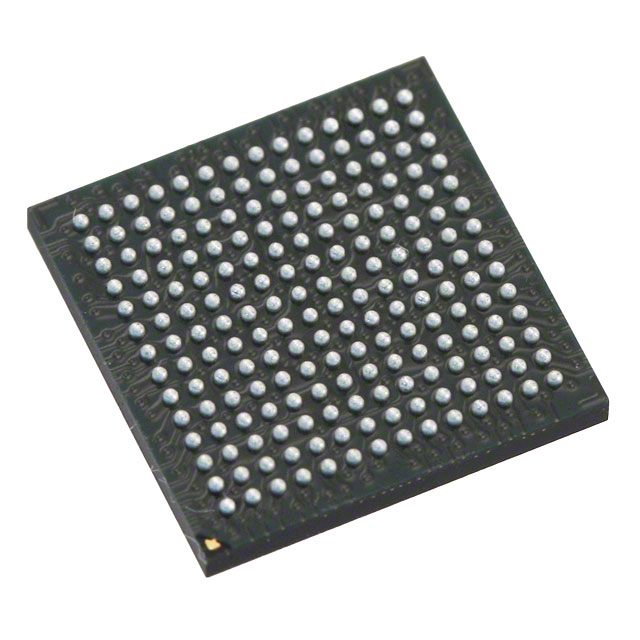

| genus | Integrated Circuit (IC) Embedded - FPGA (porta agri Programmabilis Forum) |

| manufacturer | Intel Xilinx |

| series | Spartan®-6 LX |

| sarcina | lance |

| productum status | in stirpe |

| Numerus LAB/CLB | 300 |

| Numerus elementorum logicae / unitates | 3840 |

| Summa ram bits | 221184 |

| I / O comitem | 106 |

| Voltage - Powered | 1.14V ~ 1.26V |

| genus institutionem | Superficiem Monte Type |

| Operating Temperature | 0°C ~ 85°C (TJ) |

| Sarcina / clausura | 196-TFBGA, CSBGA |

| Supplementum Fabrica Packaging | 196-CSPBGA (8x8) |

| Basic productum numerus | XC6SLX4 |

referre ugbay

Environment et Exporting Classification

| ATTRIBUTES | PERSEQUOR |

| RoHS status | Obsequium ROHS3 specificationem |

| Humorem Sensitivum Level (MSL) | III (CLXVIII horas) |

| SPATIUM status | Non products SPATIUM |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

Notae:

1. Accentus ultra eos qui sub Absoluto maximorum Rating recensentur, posset detrimentum permanentem in fabrica facere.Hi sunt accentus ratings

tantum, et operativa operatio machinae in his vel quibusvis aliis conditionibus ultra ea quae sub Conditionibus Operating recensentur, non importatur.

Patefacio ut Absolutae Maximae Ratings condiciones per longius temporis spatia afficerent artificium constantiae.

2. Cum programmatum eFUSE, VFS ≤ VCCAUX.Requirit usque ad 40 mA currentis.Nam modus legitur, VFS esse inter GND et 3.45 V.

3. I/O maximum absolutum DC et AC significationibus modum applicatum.LUXURIA durationis recipis a data periodo ut I / O illustratur

supra 3.45V.

4. For I/O operatio, refer ad UG381: Spartan-6 FPGA SelectIO Resources User Guide.

5. Maximum percent LUXURIA durationis ad maximum 4.40V occurrit.

6. TSOL est maxima solidaria temperatura pro corporibus componentibus.Ad lineamenta solidandas et scelerisque speculationes;

vide UG385: Spartan-6 FPGA Packaging and Pinout Specification.

Commendatur Operating Conditions (I)

Descriptio symboli Min Typ Max Unitates

VCCINT

Internum copiam intentionis respectu GND

-3, -3N, -2 Latin performance (2).

1.14 1.2 1.26 V

-3, -2, -2

1.2 1.23 1.26 V

-1L Standard performance (2)

0.95 1.0 1.05 V

VCCAUX (3) (4) Auxiliares copiae intentionis ad GND

VCCAUX = 2.5V(5)

2.375 2.5 2.625 V

VCCAUX = 3.3V 3.15 3.3 3.45 V

VCCO(6)(7)(8) Output copia intentionis GND 1.1 – 3.45 V

VIN

Input intentione respectu GND

Omnes EGO / O *

signa

(praeter PCI)

Commercial temperatus (C) -0.5 - 4.0 V

Temperatus industrialis (I) -0.5 - 3.95 V

Expanded (Q) temperatus -0.5 - 3.95 V

PCI I/O vexillum(9)

-0.5 - VCCO + 0.5 V

IIN (10)

Maxime current per pin utens PCI I / O vexillum

cum deinceps biasing Fibulae diode. (IX)

Commercial (C) et

Temperatus industrialis (I)

- - 10 mA

Expanded (Q) temperatus - - 7 mA

Maximam venam per clavum cum fibulae diode progrediens bilinguis humum.- - 10 mA

VBATT (11)

Pugna intentione ad GND, Tj = 0°C ad +85°C

(LX75, LX75T, LX100, LX100T, LX150, et LX150T only)

1.0 - 3.6 V

Tj

Coniunctiones temperatus operating range

Commercial (C) range 0 - 85 °C

Temperatus industrialis (I) range -40 - 100 °C

Expanded (Q) temperatus range -40 - 125 °C

Notae:

1. Omnes intentiones ad terram relati sunt.

2. Vide interface euismod pro Memoria interfaces in Tabula 25. Protracta perficiendi range specificatur pro consiliis non utens

vexillum VCCINT intentione patens.VCCINT in intentione vexillum ponitur pro:

• cogitationes quae non utuntur in MCB

• LX4 cogitationes

• machinae in TQG144 vel CPG196 packages

• machinae cum -3N celeritate gradus

3. Commendatur maxima intentione demissa pro VCCAUX est 10 mV/ms.

4. In configuratione, si VCCO_2 sit 1.8V, debet esse VCCAUX 2.5V.

5. -1L machinis quaerunt VCCAUX = 2.5V cum adhibitis LVDS_25, LVDS_33, BLVDS_25, LVPECL_25, RSDS_25, RSDS33, PPDS_25;

et PPDS_33 I/O signa in initibus.LVPECL_33 non valet in -1L machinis.

6. Configurationis notitia retinetur etiam si VCCO guttae ad 0V.

7. Includes VCCO of 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V.

8. Pro systematis PCI, transfusor et receptor communes commeatus VCCO habere debent.

9. machinae cum gradu celeritatis -1L non sustinent Xilinx PCI IP.

10. Ne summam 100 mA per ripam excedant.

11. VBATT conservare debebit altilium RAM subnixos (BBR) AES clavem cum VCCAUX non applicatur.Semel VCCAUX adhibetur, VBATT potest esse

alienus.Cum BBR non adhibetur, Xilinx cum VCCAUX vel GND suadet connectens.Sed VBATT seiungi potest.